# SOSA™ Aligned Power Supply SOS028x3U301yzzz

# SOSA-Aligned DC-DC Converter

#### **Features & Benefits**

- Open VPX VITA 62

- 10 45V input voltage range

- 300W output power

- 3U Open VPX power supply

- Conduction cooled

- I<sup>2</sup>C IPMI 46.11 monitoring and control

- · Input voltage reverse-polarity protection

- Remote voltage sensing for +12V and +3.3V auxiliary

- Parallel operation capable with proprietary wireless current sharing

- Overcurrent, overvoltage and overtemperature protections

- IPC-A-610 class 3

- No aluminum electrolytic capacitors

- Enable, inhibit, system reset and power fail controls

- Meets military standard compliance: [a]

- MIL-STD-704F

- MIL-STD-461G

- MIL-STD-810G

- MIL-STD-1275E

- RTCA/DO-160G

## **Typical Applications**

- VPX power modules

- Avionics

- Shipborne electronics

## **Product Description**

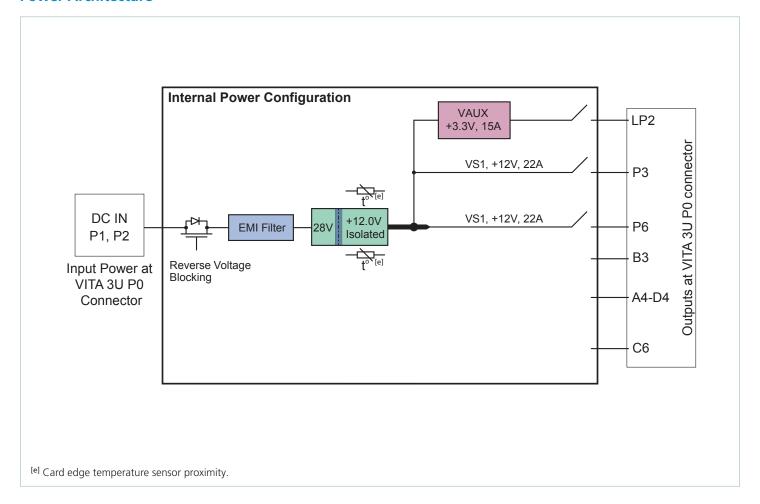

The Vicor SOSA-aligned power supply is a COTs power supply that is designed for 3U Open VPX systems that are developed to the SOSA standard. The module utilizes Vicor proprietary technology to enable high efficiency and power density for this highly rugged, conduction-cooled model.

Up to four power supplies can be paralleled to increase output power capability of  $\pm 12V$  main and  $\pm 3.3V$  auxiliary outputs with proprietary wireless current sharing. Need for conventional current-share pins are eliminated. Current share accuracy is  $\pm 2A$ .

Note: Product images may not highlight current product markings and cosmetic features.

<sup>[</sup>a] See detailed specifications; contact Vicor Applications Engineering for report details.

# **Connector Pin Configuration**

| DOME | ROWS POWER |           |     | SIGNAL |   |   |   |   |   | DOWED |   |       |    |       |     |    |

|------|------------|-----------|-----|--------|---|---|---|---|---|-------|---|-------|----|-------|-----|----|

| ROWS | P(         | JVVE      | .K  | 1      | 2 | 3 | 4 | 5 | 6 | 7     | 8 | POWER |    |       |     |    |

| D    |            |           |     |        |   |   |   |   |   |       |   |       |    |       |     |    |

| С    | P1         | DΩ        | LP1 |        |   |   |   |   |   |       |   | P3    |    | P4 P5 | LP2 | DG |

| В    | ГІ         | <b>FZ</b> | LFI |        |   |   |   |   |   |       |   |       | Γ4 |       |     | F0 |

| Α    |            |           |     |        |   |   |   |   |   |       |   |       |    |       |     |    |

|      |            |           |     |        |   |   |   |   |   |       |   |       |    |       |     |    |

**3U P0 Connector**

Note: See mechanical drawing on page 30 for connector information.

# **Connector Pin Descriptions**

| Pin            | Function / Name              | Description                                                                                               |

|----------------|------------------------------|-----------------------------------------------------------------------------------------------------------|

| P1             | -DC_IN                       | V <sub>IN</sub> -                                                                                         |

| P2             | +DC_IN                       | V <sub>IN+</sub>                                                                                          |

| LP1            | CHASSIS                      | Chassis                                                                                                   |

| A1, B1, C1, D1 | No Connection                |                                                                                                           |

| A2             | No Connection                |                                                                                                           |

| B2             | FAIL*                        | When any of the output is not within specification, FAIL* signal will be driven low to indicate a failure |

| C2             | INHIBIT*                     | Input control signal as defined in VITA 62, referenced to SIGNAL_RETURN                                   |

| D2             | ENABLE*                      | Input control signal as defined in VITA 62, referenced to SIGNAL_RETURN                                   |

| A3, B3, C3, D3 | No Connection                |                                                                                                           |

| A4, B4, C4, D4 | No Connection                |                                                                                                           |

| A5             | *GA0                         | Geographical address defined by VITA 46.11                                                                |

| B5             | *GA1                         | Geographical address defined by VITA 46.11                                                                |

| C5             | SM0 (I <sup>2</sup> C Clock) | Drim and 12C communication has                                                                            |

| D5             | SM1 (I <sup>2</sup> C Data)  | Primary I <sup>2</sup> C communication bus                                                                |

| A6             | I <sup>2</sup> C Clock       | Redundant I <sup>2</sup> C communication bus                                                              |

| В6             | I <sup>2</sup> C Data        | Redundant I-C communication bus                                                                           |

| C6             | No Connection                |                                                                                                           |

| D6             | SYS_RESET*                   | System Reset is actively low. It will float when all outputs are within specification                     |

| A7, B7, C7     | No Connection                |                                                                                                           |

| D7             | SIGNAL_RETURN                | Ground pin for control and communication signals; internally Kelvin-connected to POWER_RETURN.            |

| A8             | +12V <sub>SENSE</sub>        | VS1 sense: shall be connected at point-of-load or on the backplane to corresponding voltage output        |

| В8             | +3.3V <sub>SENSE</sub>       | VAUX sense: shall be connected at point-of-load or on the backplane to corresponding voltage output       |

| C8             | No Connection                |                                                                                                           |

| D8             | SENSE_RETURN                 | Shall be connected to POWER_RETURN either remotely or at the connector                                    |

| Р3             | VS1                          | +12V main output                                                                                          |

| P4, P5         | POWER_RETURN                 | Common output voltage return pin                                                                          |

| LP2            | VAUX                         | +3.3V auxiliary output                                                                                    |

| P6             | VS1                          | +12V main output                                                                                          |

# **Part Ordering Information**

| Part Number                       | Product Grade          | Conformal Coating                       | Factory-Configured<br>Options                                                       |

|-----------------------------------|------------------------|-----------------------------------------|-------------------------------------------------------------------------------------|

| SOS028 <b>H</b> 3U301 <b>C000</b> |                        | <b>C</b> = Coated                       | 000 = Programmable, <sup>[b]</sup> SOSA standard keying <sup>[c]</sup>              |

| SOS028 <b>H</b> 3U301 <b>D000</b> | <b>H</b> = -40 to 85°C | <b>D</b> = Coated + AU-plated Connector | SOSA standard keying [c]                                                            |

| SOS028 <b>H</b> 3U301 <b>C001</b> | <b>H</b> = -40 to 85°C | <b>C</b> = Coated                       | Programmable, [b]                                                                   |

| SOS028 <b>H</b> 3U301 <b>D001</b> |                        | <b>D</b> = Coated + AU-plated Connector | <b>001</b> = Programmable, <sup>[b]</sup> VITA46 No-Key Guide Socket <sup>[c]</sup> |

<sup>[</sup>b] Programmable units can be set by the user to parallel ready or standalone operation only via I<sup>2</sup>C. Contact factory for options with no remote sense or different output voltages. See I<sup>2</sup>C user guide for information on changing the unit from Parallel operation to Standalone. By default, units are set to parallel from the factory.

# **Absolute Maximum Ratings**

The absolute maximum ratings below are stress ratings only. Operation at or beyond these maximum ratings can cause permanent damage to the device.

| Parameter                     | Comments                                                 | Min  | Max | Unit            |

|-------------------------------|----------------------------------------------------------|------|-----|-----------------|

| Total Output Power            | Combined outputs for all rails                           |      | 300 | W               |

| Operational Input Voltage     | +IN to -IN, 100V 50ms operation MIL-STD-1275E surge only | -0.5 | 100 | V               |

| Operating Temperature         | Measured at card edge                                    | -40  | 85  | 00              |

| Storage Temperature           |                                                          | -40  | 125 | °C              |

| Isolation Voltage IN to OUT   |                                                          |      | 500 | V <sub>DC</sub> |

| Isolation Voltage IN to CASE  |                                                          |      | 500 | V <sub>DC</sub> |

| Isolation Voltage OUT to CASE |                                                          |      | 100 | V <sub>DC</sub> |

<sup>&</sup>lt;sup>[c]</sup> Refer to connector components table, page 25.

# **Electrical Characteristics**

All data at nominal line and nominal load unless otherwise specified.

| Attribute                                      | Symbol                | Conditions / Notes                                                                      | Min   | Тур  | Max   | Unit              |

|------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------|-------|------|-------|-------------------|

|                                                |                       |                                                                                         |       |      |       |                   |

|                                                |                       | Overall System Characteristics                                                          |       |      |       |                   |

|                                                |                       | Nominal line, 25% aggregate loads                                                       |       | 85   |       |                   |

| System Efficiency                              |                       | Nominal line, 50% aggregate loads                                                       |       | 87.0 |       | %                 |

|                                                |                       | Nominal line, 100% aggregate loads                                                      |       | 89   |       |                   |

|                                                |                       | Power Input Characteristics                                                             |       |      |       |                   |

| Operating Input Voltage Range                  | $V_{IN}$              |                                                                                         | 10    | 28   | 45    | V                 |

| Input Current (No Load)                        | I <sub>IN-NL</sub>    | 28V Input, enable asserted, inhibit de-asserted                                         |       | 0.50 | 1.0   | А                 |

| Inrush Current                                 | I <sub>INRUSH</sub>   | Peak no load, nominal line, high line; see Figure 5                                     |       | 70   | 120   | А                 |

| Power On to +3.3V Auxiliary<br>Output Delay    |                       | If ENABLE* is tied to signal ground                                                     | 100   | 150  | 200   | ms                |

| Input Undervoltage Lockout                     |                       |                                                                                         |       |      | 9     | V                 |

| Input Undervoltage Lockout Recovery            |                       |                                                                                         |       |      | 9.5   | V                 |

|                                                |                       | VS1: +12V Output                                                                        |       |      |       |                   |

| Output Voltage Set Point                       | $V_{VS1}$             |                                                                                         | 11.85 | 12.1 | 12.15 | V                 |

| Output Regulation Over Line & Load             |                       | Standalone mode                                                                         |       | 50   |       | mV                |

|                                                |                       | Parallel mode                                                                           |       | 200  | 250   | IIIV              |

| Output Voltage Ripple / Noise                  |                       | Nominal line from 1.5A load to full load                                                |       | 50   | 120   | mV <sub>P-P</sub> |

| Rated Output Current                           | I <sub>R-VS1</sub>    | VS1 total, sourced through contact P6 or P3                                             |       |      | 22    | А                 |

| Maximum Operating<br>Transmission Voltage Drop | V <sub>TD-VS1</sub>   |                                                                                         |       |      | 0.5   | V                 |

| Maximum Output Capacitance                     | C <sub>O-VS1</sub>    |                                                                                         |       |      | 9     | mF                |

| Soft-Start Ramp Time                           | t <sub>SS-VS1</sub>   | All full load with max C <sub>O-VS1</sub>                                               |       | 10   |       | ms                |

| Overcurrent Trip Threshold                     | I <sub>OCP_VS1</sub>  | Sourced through contact P6                                                              | 24    |      |       | А                 |

|                                                |                       | VAUX: +3.3V Output                                                                      |       |      |       |                   |

| Output Voltage Set Point                       | $V_{VAUX}$            |                                                                                         | 3.25  | 3.35 | 3.45  | V                 |

| Output Regulation Over Line & Load             |                       |                                                                                         |       | 100  | 150   | mV                |

| Output Voltage Ripple / Noise                  |                       | Nominal line over load range, 20MHz BW;<br>measured with 1µF and 10µF ceramic capacitor |       |      | 50    | mV <sub>P-P</sub> |

| Rated Output Current                           | I <sub>R-VAUX</sub>   |                                                                                         |       |      | 15    | А                 |

| Maximum Output Capacitance                     | C <sub>O-VAUX</sub>   |                                                                                         |       |      | 5     | mF                |

| Soft-Start Ramp Time                           | t <sub>SS-VAUX</sub>  | All full load with max C <sub>O-VAUX</sub>                                              |       |      | 5     | ms                |

| Overcurrent Trip Threshold                     | I <sub>OCP_VAUX</sub> |                                                                                         | 18    |      |       | А                 |

# **Signal Characteristics**

All of the following plots are at nominal line and 600W aggregate load unless otherwise noted.

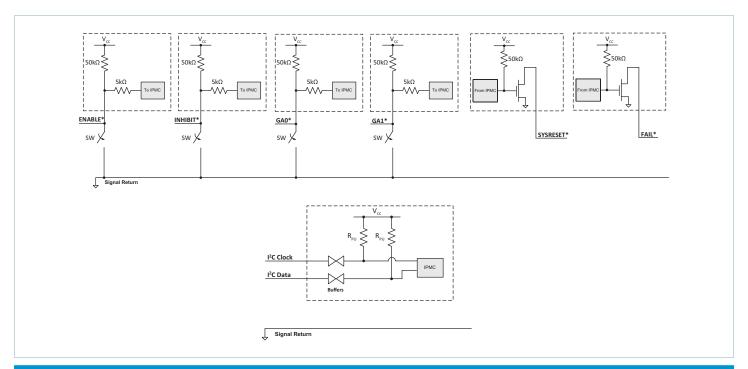

#### **ENABLE\*: Enable\***

- The ENABLE\* pin or control register bit enables and disables the +3.3V AUX output of the power supply.

- The ENABLE\* pin has an internal pull-up to VCC and is referenced to the Signal Return pin of the power supply.

| Signal Type      | State | Attribute                                                 | Symbol                  | Conditions / Notes | Min  | Тур  | Max  | Unit |

|------------------|-------|-----------------------------------------------------------|-------------------------|--------------------|------|------|------|------|

|                  |       | ENABLE* Enable Threshold                                  | V <sub>ENABLE-EN</sub>  |                    |      |      | 0.8  | V    |

|                  |       | ENABLE*<br>Disable Threshold                              | V <sub>ENABLE-DIS</sub> |                    | 2.0  |      |      | V    |

|                  |       | Internally Generated V <sub>CC</sub>                      | $V_{CC}$                |                    | 3.21 | 3.30 | 3.39 | V    |

| Digital<br>Input | Any   | ENABLE* Internal Pull-Up<br>Resistance to V <sub>CC</sub> | R <sub>ENABLE-INT</sub> |                    | 49   | 51   | 52   | kΩ   |

|                  |       | ENABLE* Enable<br>Debounce Delay                          | t <sub>D-EN-E</sub>     |                    | 3    | 5    |      | ms   |

|                  |       | ENABLE* Disable<br>Debounce Delay                         | t <sub>D-EN-D</sub>     |                    | 3    | 5    |      | ms   |

## INHIBIT\*: Inhibit\*

- ullet The INHIBIT\* pin enables and disables all outputs except +3.3V<sub>AUX</sub> if V<sub>ENABLE-EN</sub> threshold has been met.

- The INHIBIT\* pin has an internal pull up to V<sub>CC</sub> and is referenced to the Signal Return pin of the power supply.

| Signal Type      | State | Attribute                                                  | Symbol                   | Conditions / Notes | Min  | Тур  | Max  | Unit |

|------------------|-------|------------------------------------------------------------|--------------------------|--------------------|------|------|------|------|

|                  |       | INHIBIT* Enable Threshold                                  | V <sub>INHIBIT-EN</sub>  |                    |      |      |      | V    |

|                  |       | INHIBIT* Disable Threshold                                 | $V_{\text{INHIBIT-DIS}}$ |                    |      |      | 0.8  | V    |

|                  |       | Internally Generated V <sub>CC</sub>                       | V <sub>CC</sub>          |                    | 3.21 | 3.30 | 3.39 | V    |

| Dinisal          |       | INHIBIT* Internal Pull-Up<br>Resistance to V <sub>CC</sub> | R <sub>DISABLE-INT</sub> |                    | 49   | 51   | 52   | kΩ   |

| Digital<br>Input | Any   | INHIBIT* Enable Debounce<br>Delay after ENABLE*            | t <sub>D-IN-E</sub>      |                    | 3    | 5    |      | ms   |

|                  |       | INHIBIT* Disable<br>Debounce Delay                         | t <sub>D-IN-D</sub>      |                    | 3    | 5    |      | ms   |

|                  |       | Lockout Delay<br>Between Consecutive<br>INHIBIT* Enables   | t <sub>D-IN-L</sub>      |                    | 3    | 5    |      | ms   |

# **Signal Characteristics (Cont.)**

All of the following plots are at nominal line and 600W aggregate load unless otherwise noted.

## GA0\*, GA1\*: Geographical Address

- The GAO\* and GA1\* pins sets the I<sup>2</sup>C address of the power supply. Geographical address is set at start up and cannot be changed without a power cycle.

- The GAO\* and GA1\* pins have an internal pull-up to V<sub>CC</sub> and is referenced to the Signal Return pin of the power supply.

| Signal Type      | State    | Attribute                                                 | Symbol                | Conditions / Notes | Min  | Тур  | Max  | Unit |

|------------------|----------|-----------------------------------------------------------|-----------------------|--------------------|------|------|------|------|

|                  |          | Address Pins Low<br>Threshold                             | $V_{ADDR-L}$          |                    |      |      | 0.8  | V    |

|                  |          | Address Pins High<br>Threshold                            | $V_{ADDR-H}$          |                    | 2.0  |      |      | V    |

| Digital<br>Input | Start Up | Internally Generated V <sub>CC</sub>                      | $V_{CC}$              |                    | 3.21 | 3.30 | 3.39 | V    |

| mpat             |          | ENABLE* Internal Pull-Up<br>Resistance to V <sub>CC</sub> | R <sub>ADDR-INT</sub> |                    | 49   | 51   | 52   | kΩ   |

|                  |          | Address Pins<br>Debounce Delay                            | t <sub>D-ADDR</sub>   |                    | 5    |      |      | ms   |

#### FAIL\*, SYSRESET\* & LED

- The power supply has one two color LED located on the ejector edge of the power supply.

- The LED is either GREEN or RED depending on the state of operation. FAIL\* and SYSRESET\* lines are set with the LED.

| Signal Type | State                              | Attribute | Symbol              | Conditions / Notes                                                                                                                                                                                           | Min | Тур | Max | Unit |

|-------------|------------------------------------|-----------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|             | Steady                             | SYSRESET* | V <sub>SYSRST</sub> | Start up: input voltage operating threshold $V_{\text{UV-IN}} < V_{\text{IN}} < V_{\text{OV-IN}}$ has been met; if steady RED persists for >100ms, a critical system fault has been detected during start up |     |     | 0.8 | V    |

| RED         | RED                                | FAIL*     | $V_{FAIL}$          |                                                                                                                                                                                                              |     |     | 0.8 | V    |

|             | Blinking                           | SYSRESET* | V <sub>SYSRST</sub> | >100ms after V <sub>UV-IN</sub> < V <sub>IN</sub> < V <sub>OV-IN</sub> has been                                                                                                                              | 2.0 |     | 3.5 | V    |

|             | GREEN                              | FAIL*     | $V_{FAIL}$          | met; power supply is ready for use                                                                                                                                                                           |     |     | 3.5 | V    |

|             | Steady                             | SYSRESET* | V <sub>SYSRST</sub> | All outputs are OK and ENABLE* is pulled low                                                                                                                                                                 |     |     | 3.5 | V    |

| Outputs     | GREEN                              | FAIL*     | $V_{FAIL}$          |                                                                                                                                                                                                              |     |     | 3.5 | V    |

|             | Blinking                           | SYSRESET* | $V_{SYSRST}$        | Power supply has encountered a OT, OV, UV, OC or critical system failure during operating                                                                                                                    |     |     | 3.5 | V    |

|             | RED                                | FAIL*     | $V_{FAIL}$          |                                                                                                                                                                                                              |     |     | 0.8 | V    |

|             | Fast Blinking<br>GREEN             | None      | -                   | SW priority is set by 0x55 status command                                                                                                                                                                    | -   | -   | -   | -    |

|             | Blinking<br>Alternate<br>GREEN/RED | None      | -                   | Battle Override mode is enabled successfully by 0x55 status command                                                                                                                                          | -   | -   | -   | -    |

# **Application Characteristics**

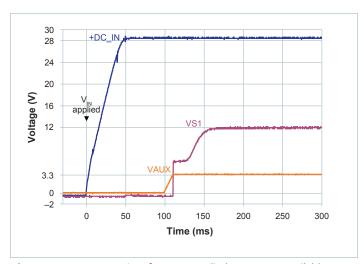

**Figure 1** — Response time from  $V_{IN}$  applied to outputs available; under 200ms start;  $V_{IN} = 28V$

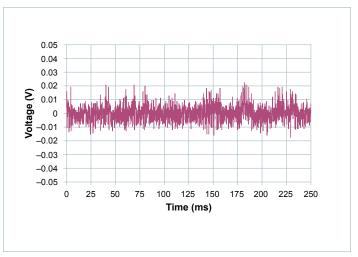

Figure 3 — AUX (+3.3V) ripple, AC-coupled

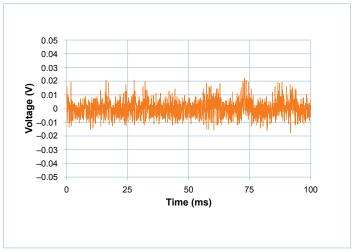

Figure 2 — VS1 (+12V) ripple at 10% load (2A), AC-coupled

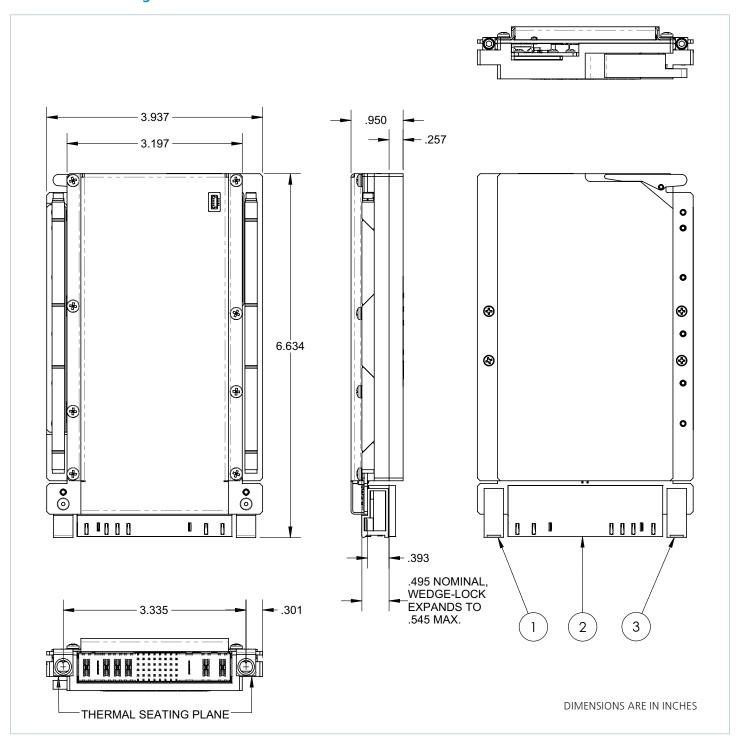

# **General Characteristics**

| Attribute             | Symbol                   | Conditions / Notes                                                                      | Min | Тур     | Max | Unit   |  |  |  |

|-----------------------|--------------------------|-----------------------------------------------------------------------------------------|-----|---------|-----|--------|--|--|--|

|                       |                          |                                                                                         |     |         |     |        |  |  |  |

|                       |                          | Mechanical                                                                              |     |         |     |        |  |  |  |

| Length                | L                        | Per VITA62                                                                              |     | 6.634   |     | in     |  |  |  |

| Width                 | W                        | Per VITA62                                                                              |     | 3.937   |     | in     |  |  |  |

| Height                | Н                        | Per VITA62                                                                              |     | 0.951   |     | in     |  |  |  |

| Weight                | W                        |                                                                                         |     | 630     |     | g      |  |  |  |

| Wedge-Lock Torque     |                          | Manufacturer's recommended value                                                        |     | 7       |     | in·lbs |  |  |  |

|                       |                          |                                                                                         |     |         |     |        |  |  |  |

| Thermal               |                          |                                                                                         |     |         |     |        |  |  |  |

| Operating Temperature | T <sub>WEDGE-LOCKS</sub> |                                                                                         | -40 |         | 85  | °C     |  |  |  |

|                       |                          |                                                                                         |     |         |     |        |  |  |  |

|                       |                          | Assembly                                                                                |     |         |     |        |  |  |  |

| Storage Temperature   |                          |                                                                                         | -40 |         | 125 | °C     |  |  |  |

|                       |                          |                                                                                         |     |         |     |        |  |  |  |

|                       |                          | Safety                                                                                  |     |         |     |        |  |  |  |

| MTBF                  |                          | MIL-HDBK-217Plus Parts Count - 25°C<br>Ground Benign, Stationary,<br>Indoors / Computer |     | 612,741 |     | Hrs    |  |  |  |

|                       |                          | Telcordia Issue 2 - Method I Case III; 25°C<br>Ground Benign, Controlled                |     | 854,689 |     | Hrs    |  |  |  |

## **Signal Pin Functions**

#### **ENABLE\* & INHIBIT\***

Enable and Inhibit pins express active low logic. Table 1 has the truth table for the output state of the power supply. It is necessary to avoid the indeterminate output state where 0.8-2.0V is applied to the ENABLE\* or INHIBIT\* pins.

A digital debounce filter is present on the signals of both pins to prevent false transitions. The ENABLE\* and INHIBIT\* also have a minimum delay between successive output enable transitions to prevent repeated starts into high capacitance loads. See detailed specifications for delays time limits.

| ENABLE* Pin                        | INHIBIT* Pin                        | Output State and Notes                        |  |  |  |

|------------------------------------|-------------------------------------|-----------------------------------------------|--|--|--|

| < 0.8V, Logic 0                    | > 2.0V or NO, Logic 1               | All outputs available                         |  |  |  |

| < 0.8V, Logic 0                    | < 0.8V, Logic 0                     | Only +3.3V <sub>AUX</sub><br>output available |  |  |  |

| > 2.0V or NO, Logic 1              | Any                                 | All outputs disabled                          |  |  |  |

| 0.8V > V <sub>ENABLE*</sub> < 2.0V | 0.8V > V <sub>INHIBIT*</sub> < 2.0V | Indeterminate state and must be avoided       |  |  |  |

Table 1 — ENABLE & INHIBIT logic

#### Geographical Address: GA0\* & GA1\*

Geographical address pins also exhibit active low logic. Table 2 has the truth table for the output state of the power supply. It is necessary to avoid the indeterminate state where 0.8 – 2.0V is applied to either address pins. A digital debounce filter is present on the signals of both pins to incorrect address assignment.

The geographical address is static and set on power up. The power supply's address cannot not change until power has been cycled and the states of the address pins have been modified before power up.

| GA1*                            | GA0*                     | Power Supply Address                    |  |  |  |

|---------------------------------|--------------------------|-----------------------------------------|--|--|--|

| > 2.0V or NO, Logic 1           | > 2.0V or NO, Logic 1    | 20h                                     |  |  |  |

| > 2.0V or NO, Logic 1           | < 0.8V, Logic 0          | 21h                                     |  |  |  |

| < 0.8V, Logic 0                 | > 2.0V or NO, Logic 1    | 22h                                     |  |  |  |

| < 0.8V, Logic 0                 | < 0.8V, Logic 0          | 23h                                     |  |  |  |

| 0.8V > V <sub>GA1*</sub> < 2.0V | $0.8V > V_{GA0*} < 2.0V$ | Indeterminate state and must be avoided |  |  |  |

**Table 2** — Geographical address assignment

#### I<sup>2</sup>C Ports:

Both primary and redundant I<sup>2</sup>C ports have the same address set by the Geographical Address pins and identical functionality. There is a bidirectional buffer on both clock and data lines with internal pull ups on the IPMC and external pulls on the back plane to +3.3V are required.

#### FAII\*

This signal line is open drain and tracks SYSRESET\* when the unit is powering up or pulled down to SIGNAL\_RETURN when any of the outputs are out of specification. A pull up resistor is expected on the backplane per section 4.6.3.7 of VITA 62.

#### SYSRESET\*

This signal line is open drain and is pulled down to SIGNAL\_RETURN when the unit is powering up. The line is released when the power supply is ready for control. Appropriate pull-up/pull-down resistors are expected on the back plane per VITA 46 section 7.3.9.

#### **SIGNAL RETURN**

SIGNAL RETURN is used as the reference for signals pin connections and is to be tied to POWER\_RETURN on the backplane per section 4.6.3.10-1 of VITA 62.

# Typical External Circuits for Signal Pins (ENABLE\*, INHIBIT\*, GA0\*, GA1\*, SYSRESET\*, FAIL\* and I<sup>2</sup>C Channels)

## **Card Edge Temperature Sensors**

The PCBA card edge temperature sensor internal to the power supply is mounted on the edge of the PCBA card edge. Consequently, the temperature sensor measures a temperature that is generally higher than the heat-sink-to-rail mounting interface and lower than the hot spot of the internal converters in the power supply.

Response from the power supply to I<sup>2</sup>C command 0x21 provides the temperature measured by the internal sensor that reads the higher temperature. This temperature can exceed 85°C. I<sup>2</sup>C command 0x92 will respond with both PCB mounted temperature sensors.

## **Fault Operation**

See Table 5 for nonrecoverable fault thresholds which trigger a fault and shut down/restart of the outputs of the supply.

#### **Input Voltage Protection (IOVP)**

If the input voltage to the power supply drops below  $V_{UV-IN}$  or exceeds  $V_{OV-IN}$  for at least 1ms, the power supply will shut down all outputs and digital communication lines until input voltage is within operating range  $V_{IN}$ . Triggering  $I_{OVP}$  has the same effect as power cycling the power supply. Supply currents and voltages are sampled every 200 $\mu$ s.

#### **Output Voltage Protection (OOVP)**

The power supply measures voltage from the remote-sense lines as well as the voltages on the VITA connector which do not include remote sense drop.

The FAIL\* line will be asserted (pulled low) when output voltage at the connector of the power supply is greater than the nonrecoverable limit of any output. OVP will also shut down the outputs until the output voltage of the converter is within specification. The power supply will automatically restart the outputs every 1s until the fault clears.

#### **Overcurrent Protection (OCP)\***

During an overcurrent fault on any output, all outputs will shut off and the FAIL\* line will be asserted. The power supply will automatically try to restart outputs every 1s if the fault has cleared.

#### **Overtemperature Protection (OTP)**

The power supply will go into overtemperature protection and shut down all outputs when either internal temperature sensor measures 95°C. The power converter will recover for normal operation when the internal temperature has dropped by 20°C.

At 85°C the Bit-5 of the Status Register (0x55) will clear if the system manager sets Bit-5 to 1 which will indicate the power supply is within 10°C from shutting down.

## **Parallel Operation**

For proper load regulation and paralleling of SOS028x3U301yzzz power supplies, sense lines shall be connected to the load. An open or unconnected sense line will lead to a fault condition where all outputs remain off. A single kelvin connection between each sense pin and load is ideal on the backplane. Another method of connecting sense lines to the load is to bus sense lines between the power supplies and have a single backplane connection to the point-of-load. Under normal parallel power supply operation, each supply's PoL regulated output will be at different voltage with respect to its own backplane connector to compensate for transmission voltage drop. Figure 4a depicts an instance of a backplane with three power supplies where the point-of-load (PoL) sense pins on each power supply are connected.

It is not recommended to connect the PoL sense pins in a manner depicted in Figure 4b where each supply's PoL sense pins are connected to each other and also to each power supply's own PoL voltage output. In this case the system may appear to function normally temporarily but load regulation and sharing are not guaranteed.

# Required Not Recommended Sense pin connections on the backplane Connecting sense pins to each other and of a three-unit parallel array to each supply's own PoL voltage output Payload N Payload N Payload 2 Payload 2 Payload 1 Payload 1 Supply 1 Supply 1 Supply 2 Supply 2 Supply 3 Supply 3 (a) (b)

Figure 4 — Sense pin connection arrangement connects all supplies to the backplane of the array

All six outputs can be connected in parallel with the same output from other power supplies with the same part number. Only the 12V output supports load sharing.

Additional information on power supply paralleling can be found in <u>AN:801 – Parallel Operation</u>.

| Output       | Max Current vs. Paralleled Supplies |    |    |    |      |

|--------------|-------------------------------------|----|----|----|------|

|              | 1                                   | 2  | 3  | 4  | Unit |

| VS1 (+12V)   | 22                                  | 40 | 60 | 80 | А    |

| VAUX (+3.3V) | 15                                  | 15 | 15 | 15 | А    |

**Table 3** — Maximum current rating by output for parallel arrays

## **Standalone Operation**

Switching the power supply from paralleling to standalone can be done on a single-use basis or permanently by the user using I<sup>2</sup>C.

Each unit ships from the factory capable of paralleling multiple identical power supplies. If the power supply is used in standalone mode without additional identical supplies connected in parallel, the output voltages of the power supply that are shareable, namely, VS1 and VAUX, will not droop with increased current load and will regulate the output voltage close to the no-load voltage. The standalone mode of operation may be desirable in applications where output voltage tolerance requirements exceed the limits allowed by VITA 62 and only one power supply is required.

In order to set the power supply to standalone mode the byte sequence shown in Table 4 needs to be transmitted to the power supply.

| IPMB<br>Byte<br>Number | Hex<br>Byte | Comment                                                                                                                                                     |

|------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                      | 40h         | Initiation of Communication; transmit request<br>to the power supply.<br>Address byte of power supply with hardware<br>address 0x20 and LSB read/write low. |

| 1                      | 66h         | Command byte 1                                                                                                                                              |

| 2                      | 99h         | Command byte 2                                                                                                                                              |

| 3                      | 10h         | Command byte 3                                                                                                                                              |

| 5                      | F1h         | Zero checksum of IPMB bytes 1-3 and Stop Bit                                                                                                                |

**Table 4** — Byte sequence to set the power supply in standalone

To verify if the power supply is in standalone mode, VS1 remote-load sense voltage can be measured between connector pin A8 and sense return D8. The voltage between A8 and D8 will drop less than 40mV between no-load and full-load. If the power supply is in paralleling mode, VS1 remote-load sense voltage measured between connector pin A8 and sense return D8 will vary over 100mV between no-load and full-load.

To set the power supply to share mode again, command byte 3 in Table 4 needs to change to 00h. The checksum for bytes 1-3 will need to be recalculated and transmitted to the power supply. The sequence will need to be transmitted to the power supply a total of 3 times for the power supply to permanently change its mode at power up to support current share or paralleling.

To permanently change the power supply to either standalone or paralleling mode, the sequence in Table 4 with byte 3 set correctly needs to be transmitted three times consecutively. Committing the change permanently will cause the power supply to adopt the desired mode of operation from power up. If the power supply mode of operation is changed permanently, the power supply will perform a soft reboot once to store settings in its internal memory. The power supply can be switched from paralleling to standalone and vice-versa permanently up to 100,000 times due to memory wear limitations. Switching mode of operation without committing changes permanently can be done as many times as the user requires. If the mode of operation is switched without committing the change permanently, the power supply will revert to the mode of operation set permanently after a power cycle.

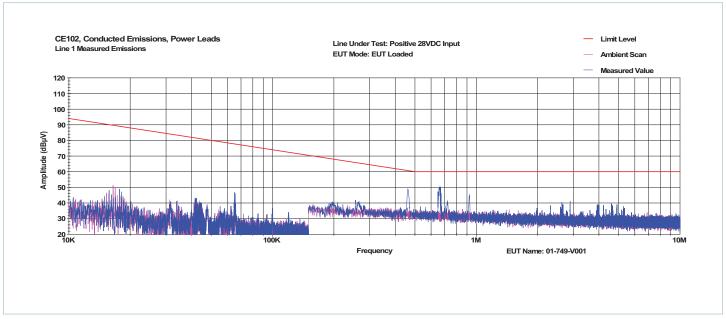

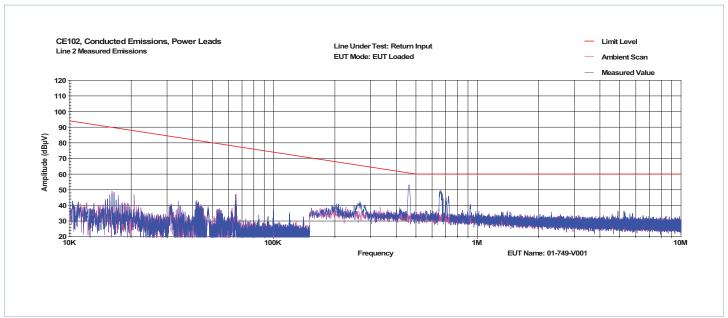

# **Conducted Emissions Testing**

Figure 5 — Conducted emissions of +28V input line at full load

Figure 6 — Conducted emissions of +28V return line at full load

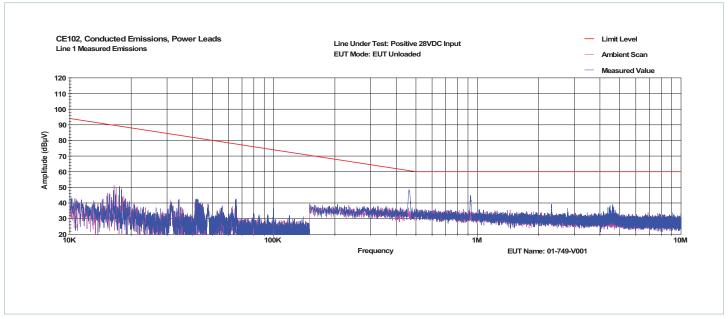

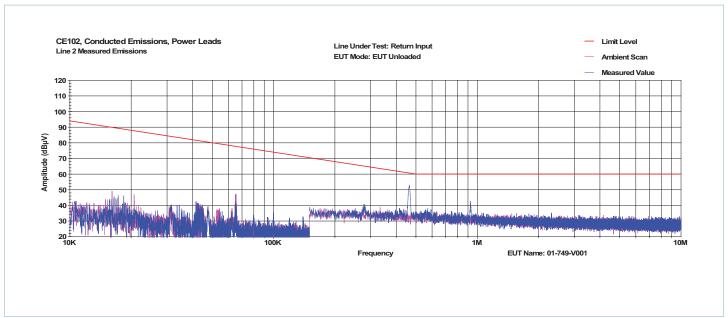

# **Conducted Emissions Testing (Cont.)**

Figure 7 — Conducted emissions of of +28V input line at no load

Figure 8 — Conducted emissions of +28V return line at no load

# **Standards Compliance**

|                                         | MIL-STD-461F                                                 |        |

|-----------------------------------------|--------------------------------------------------------------|--------|

|                                         | ±200V, 10µs                                                  | Passed |

| CS06                                    | ±400V, 5µs                                                   | Passed |

|                                         | 1000 – 2000Hz PSD decreasing at 6dB/octave                   | Passed |

|                                         | Bulk input power cables                                      | Passed |

| CS115                                   | Bulk output power cables                                     | Passed |

|                                         | Bulk input power cables                                      | Passed |

| CS116                                   | Bulk output power cables                                     | Passed |

|                                         |                                                              |        |

|                                         | MIL-STD-461G                                                 |        |

| CE102                                   | Basic curve                                                  | Passed |

| CS101                                   | Figure CS101-1, Cuve #2                                      | Passed |

| 65444.6                                 | Input power lead                                             | Passed |

| CS114 Curve 5                           | Bulk input power cables                                      | Passed |

|                                         |                                                              |        |

|                                         | MIL-STD-704F                                                 |        |

| LDC103 – Voltage Distortion Spectrum    |                                                              | Passed |

| LDC105 – Normal Voltage Transients      |                                                              | Passed |

| LDC302 – Abnormal Voltage Transients    |                                                              | Passed |

|                                         |                                                              |        |

|                                         | MIL-STD-810G                                                 |        |

|                                         | 1 – 100Hz PSD increasing at 3dB/octave                       | Passed |

| Vibration, Method 514.5 Procedure I     | 100 – 1000Hz PSD = 0.1g2/Hz                                  | Passed |

|                                         | 1000 – 2000Hz PSD decreasing at 6dB/octave                   | Passed |

| Operating Shock, Method 516 Procedure I | 40g, 11ms shock half-sine                                    | Passed |

| Operating Shock, Method 516 Procedure i | 40g, 11ms, terminal saw-tooth shock pulses in all three axes | Passed |

|                                         |                                                              |        |

|                                         | RTCA/DO-160G                                                 |        |

| Section 15: ESD                         |                                                              | Passed |

| Section 17: Voltage Spike, Category A   |                                                              | Passed |

|                                         |                                                              |        |

|                                         | IEC 61000-4-2                                                |        |

| ESD, Level 4                            | ±15kV Air Discharge                                          | Passed |

|                                         |                                                              |        |

|                                         | VITA 47                                                      |        |

| Humidity                                | Method 507 per VITA 47 Section 4.6                           | Passed |

| Operating Temperature                   | VITA 47 Section 4.1.2 class CC4                              | Passed |

| Temperature Cycling                     | MIL-STD-202 Method 107 per VITA 47 Section 4.3               | Passed |

| Altitude                                | 1,500ft below sea level to 70,000ft above sea level          | Passed |

| Fungus Resistance                       | MIL-STD-810G, Method 508 per VITA47 Section 4.10             | Passed |

| Corrosion Resistance                    | ASTM G85, Annex A4, cycle A4.4.4.1 per VITA 47 Section 4.12  | Passed |

#### I<sup>2</sup>C Sensor Commands

Commands are sent by SMBus-compatible packets over the  $I^2C$  physical interface. The  $I^2C$  bus will communicate at 100kHz. Pull-up resistors to +3.3V are expected on the system backplane.

Two pins, labeled \*GA1 and \*GA0 are provided at each power supply slot, where \*GA1 and \*GA0 are defined to be active (SET) when low. The power supply will respond to I<sup>2</sup>C address 010 00[GA1][GA0].

The power supply supports commands to read sensor data from the power supply without utilizing VITA 46.11 or IPMI. The commands are similar to register reads in from I<sup>2</sup>C memory and function in a parent/child configuration. Unlike VITA 46.11 which is a multi-parent protocol, commands defined in this section are parent-write and parent-read.

Table 5 shows the following transmission pattern for reading power supply rail temperatures with command 0x92 using the parent-write/parent-read transmission format. In all non-VITA 46.11 commands, the parent requests the data from the child, which is the power supply.

| IPMB<br>Byte<br>Number | Hex<br>Byte | Clock Pulses<br>Generated By | Data Pulses<br>Generated By | Comment                                                                                                                                              | Real Value     |

|------------------------|-------------|------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1                      | 40h         | Requestor                    | Requestor                   | Initiation of Communication; transmit request to the power supply;<br>Address byte of power supply with hardware address 0x20 and LSB read/write low |                |

| 2                      | 92h         | Requestor                    | Requestor                   | Command to read power supply temperatures                                                                                                            |                |

| 3                      | 6Eh         | Requestor                    | Requestor                   | Zero checksum generated from IPMB byte 2 (or all bytes after Address Byte up to the checksum byte)                                                   |                |

| 4                      | 41h         | Requestor                    | Requestor                   | Read response from the power supply; Address byte of power supply with hardware address 0x20 and LSB read/write high                                 |                |

| 5                      | 92h         | Requestor                    | Power Supply                | Response byte 1 Echo of the command from the reques                                                                                                  |                |

| 6                      | 01h         | Requestor                    | Power Supply                | Response byte 2                                                                                                                                      | 013Bh = 31.5°C |

| 7                      | 3Bh         | Requestor                    | Power Supply                | Response byte 3                                                                                                                                      |                |

| 8                      | 01h         | Requestor                    | Power Supply                | Response byte 4                                                                                                                                      | 0146h = 32.6°C |

| 9                      | 46h         | Requestor                    | Power Supply                | Response byte 5                                                                                                                                      |                |

| 10                     | EBh         | Requestor                    | Power Supply                | Zero checksum of IPMB bytes 6-9                                                                                                                      |                |

**Table 5** — Communication example of command non-VITA 46.11 command 0x92

Checksum bytes are 2's complement checksum of bytes in the request excluding the address byte or between the previous checksum and next checksum excluding the address byte.

## 8-bit checksum algorithm:

- 1. Initialize checksum to 0.

- For each applicable byte, checksum = (checksum + byte) modulo 256.

- 3. Then checksum = checksum.

#### Verification

When the checksum and the bytes are added together, modulo 256, the result should be 0.

Example of the checksum for the data returned by the power supply in Table 5.

$$\Leftrightarrow 256 - ((\sum_{x=5}^{9} IPMB\_Bytes x) \mod 256) = EBh$$

$$\Leftrightarrow 256 - ((92h + 01h + 3Bh + 01h + 46h) \bmod 256) = EBh$$

Verification:

$$(Ebh + (92h + 01h + 3Bh + 01h + 46h)) \mod 256 = 0$$

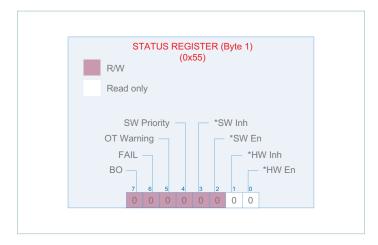

Table 6 shows how to set and read the Status Register Byte.

Checksum bytes are 2's complement checksum of bytes in the request excluding the address byte or between the previous checksum and next checksum excluding the address byte.

| IPMB<br>Byte<br>Number | Hex Byte | Clock Pulses<br>Generated By | Data Pulses<br>Generated By | Comment                                                                                                                                              | Real Value     |

|------------------------|----------|------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 0                      | 40h      | Requestor                    | Requestor                   | Initiation of Communication; transmit request to the power supply;<br>Address byte of power supply with hardware address 0x20 and LSB read/write low |                |

| 1                      | 55h      | Requestor                    | Requestor                   | Command to set the status register                                                                                                                   |                |

| 2                      | 6Eh      | Requestor                    | Requestor                   | Zero checksum generated from IPMB byte 2 (or all bytes after Address Byte up to the checksum byte)                                                   |                |

| 4                      | 41h      | Requestor                    | Requestor                   | Read response from the power supply; Address byte of power supply with hardware address 0x20 and LSB read/write high.                                |                |

| 5                      | 92h      | Requestor                    | Power Supply                | Response byte 1 Echo of the command from the reques                                                                                                  |                |

| 6                      | 01h      | Requestor                    | Power Supply                | Response byte 2                                                                                                                                      | 013Bh = 31.5°C |

| 7                      | 3Bh      | Requestor                    | Power Supply                | Response byte 3                                                                                                                                      |                |

| 8                      | 01h      | Requestor                    | Power Supply                | Response byte 4                                                                                                                                      | 0146h = 32.6,C |

| 9                      | 46h      | Requestor                    | Power Supply                | Response byte 5                                                                                                                                      |                |

| 10                     | EBh      | Requestor                    | Power Supply                | Zero checksum of IPMB bytes 6-9                                                                                                                      |                |

**Table 6** — Communication example of status register byte

## **Commands Recognized by Power Supply**

| 0x21: Sensor Data (Read Only) [d] |                        |          |                                                                                               |  |  |  |

|-----------------------------------|------------------------|----------|-----------------------------------------------------------------------------------------------|--|--|--|

|                                   |                        |          |                                                                                               |  |  |  |

| Byte<br>Number                    | Contents               | Format   | Scaling                                                                                       |  |  |  |

| 0                                 | 0x21                   | Byte     | Echo of the command                                                                           |  |  |  |

| 1                                 | Status Reg             | Byte     | See below, same as used by command 0x55                                                       |  |  |  |

| 2, 3                              | PCBA Temperature °C    | INT16    | 16384 = 100°C                                                                                 |  |  |  |

| 4, 5                              | +12V VSENSE            | UINT16   | 16384 = 12.0V                                                                                 |  |  |  |

| 6, 7                              | Not Used               | UINT16   |                                                                                               |  |  |  |

| 8, 9                              | Not Used               | UINT16   |                                                                                               |  |  |  |

| 10, 11                            | +3.3VAUX VSENSE        | UINT16   | 16384 = 3.3V                                                                                  |  |  |  |

| 12, 13                            | Not Used               | UINT16   |                                                                                               |  |  |  |

| 14, 15                            | Not Used               | UINT16   |                                                                                               |  |  |  |

| 16, 17                            | +12V IOUT (contact P6) | UINT16   | 16384 = 40A                                                                                   |  |  |  |

| 18, 19                            | Not Used               | UINT16   |                                                                                               |  |  |  |

| 20, 21                            | +12V IOUT (contact P3) | UINT16   | 16384 = 40A                                                                                   |  |  |  |

| 22, 23                            | +3.3VAUX IOUT          | UINT16   | 16384 = 15A                                                                                   |  |  |  |

| 24, 25                            | Not Used               | UINT16   |                                                                                               |  |  |  |

| 26, 27                            | Not Used               | UINT16   |                                                                                               |  |  |  |

| 28, 29                            | Not Used               | UINT16   |                                                                                               |  |  |  |

| 30, 31                            | Input Voltage          | UINT16   | 16384 = 28V                                                                                   |  |  |  |

| 32 – 51                           | Part Number            | CHAR[20] | no 0 term, padded with 0x20                                                                   |  |  |  |

| 52 – 55                           | Serial Number          | UINT32   | Unsigned 32-bit integer;<br>last 9 digits of the serial<br>number of the unit on the<br>label |  |  |  |

| 56, 57                            | Factory Use Only       | UINT16   | N/A: factory use only                                                                         |  |  |  |

| 58, 59                            | Hardware Rev           | CHAR[2]  |                                                                                               |  |  |  |

| 60, 61                            | Firmware Rev           | CHAR[2]  |                                                                                               |  |  |  |

| 62                                | Input Current          | UINT8    | 255 = 80A                                                                                     |  |  |  |

| 63                                | Zero Checksum          | Byte     | Sum(Bytes 0:63) mod 256<br>= 0                                                                |  |  |  |

<sup>&</sup>lt;sup>[d]</sup> Most-significant bit of each byte is transmitted first.

Most-significant byte of UINT16 and UINT32 transmitted first.

# Non-VITA 46.11 Recognized by Power Supply

|                                        | 0x44: Firmware Date (Read Only) [d] |           |                                |  |  |  |

|----------------------------------------|-------------------------------------|-----------|--------------------------------|--|--|--|

| • 22 byte                              | response in ASCII fo                | rm.       |                                |  |  |  |

| Byte<br>Number                         | Contents                            | Format    | Typical Value/Comment          |  |  |  |

| 0                                      | 0x44                                | Byte      | Echo of the command            |  |  |  |

| 1 – 20                                 | Date                                | ASCII[20] | 'NOV 28 14:32:54 2018'         |  |  |  |

| 21                                     | Zero Checksum                       | Byte      | Sum(Bytes 0:21)<br>mod 256 = 0 |  |  |  |

|                                        |                                     |           |                                |  |  |  |

| 0x45: Hardware Address (Read Only) [d] |                                     |           |                                |  |  |  |

|                                        |                                     |           |                                |  |  |  |

| _                                      |                                     |           |                                |  |  |  |

| Byte<br>Number | Contents                 | Format | Typical Value/Comment         |

|----------------|--------------------------|--------|-------------------------------|

| 0              | 0x45                     | Byte   |                               |

| 1              | I <sup>2</sup> C Address | Byte   | 0x23,<br>set by *GA1, *GA0    |

| 2              | Zero Checksum            | Byte   | Sum(Bytes 0:2)<br>mod 256 = 0 |

# 0x55: Status Command (Read/Write) [d]

| Byte<br>Number | Contents      | Format | Typical Value/Comment         |

|----------------|---------------|--------|-------------------------------|

| 0              | 0x55          | Byte   |                               |

| 1              | Status Byte   | Byte   | 0x18 = All outputs ON         |

| 2              | Zero Checksum | Byte   | Sum(Bytes 0:2)<br>mod 256 = 0 |

# 0x90: All Voltages in mV (Read Only) [d]

| Byte<br>Number | Contents       | Format | Scaling/Comment                |

|----------------|----------------|--------|--------------------------------|

| 0              | 0x90           | Byte   | Echo of the command            |

| 1, 2           | +12V SENSE     | UINT16 | 10mV/bit                       |

| 3, 4           | Not Used       | UINT16 |                                |

| 5, 6           | Not Used       | UINT16 |                                |

| 7, 8           | +3.3VAUX SENSE | UINT16 | 10mV/bit                       |

| 9, 10          | Not Used       | UINT16 |                                |

| 11, 12         | Not Used       | UINT16 |                                |

| 13, 14         | Input Voltage  | UINT16 | 10mV/bit                       |

| 15             | Zero Checksum  | Byte   | Sum(Bytes 0:15)<br>mod 256 = 0 |

# Non-VITA 46.11 Recognized by Power Supply (Cont.)

| 0,000, 1/01 | Output and | Innut Current | in m 1   | (Read Only) [d] |

|-------------|------------|---------------|----------|-----------------|

| UX33. V31   | Output and | inbut current | III IIIA | thead Only      |

| Byte<br>Number | Contents      | Format | Scaling/Comment               |

|----------------|---------------|--------|-------------------------------|

| 0              | 0x99          | Byte   | Echo of the command           |

| 1, 2           | +12V IOUT     | UINT16 | 10mA/bit                      |

| 3, 4           | Not Used      | UINT16 |                               |

| 5, 6           | Not Used      | UINT16 |                               |

| 7, 8           | Input Current | UINT16 | 10mA/bit                      |

| 9              | Zero Checksum | Byte   | Sum(Bytes 0:9)<br>mod 256 = 0 |

## 0x91: VAUX Output Current in mA (Read Only) [d]

| Byte<br>Number | Contents      | Format | Scaling/Comment               |

|----------------|---------------|--------|-------------------------------|

| 0              | 0x91          | Byte   | Echo of the command           |

| 1, 2           | +3.3VAUX IOUT | UINT16 | 1mA/bit                       |

| 3, 4           | Not Used      | UINT16 |                               |

| 5, 6           | Not Used      | UINT16 |                               |

| 7              | Zero Checksum | Byte   | Sum(Bytes 0:7)<br>mod 256 = 0 |

## 0x92: PCBA Card Edge Temperatures in °C x 10 (Read Only) [d]

| Byte<br>Number | Contents                         | Format | Scaling/Comment                         |

|----------------|----------------------------------|--------|-----------------------------------------|

| 0              | 0x92                             | Byte   | Echo of the command                     |

| 1, 2           | 3U P0 connector,<br>P1 side Rail | INT16  | Temperature x 10,<br>eg. −123 = −12.3°C |

| 3, 4           | 3U P0 connector,<br>P6 side Rail | INT16  | Same as above                           |

| 5              | Zero Checksum                    | Byte   | Sum(Bytes 0:5)<br>mod 256 = 0           |

<sup>&</sup>lt;sup>[d]</sup> Most-significant bit of each byte is transmitted first.

Most-significant byte of UINT16 and UINT32 transmitted first.

## Status Register Bit Map used in command 0x55

Bit 0 and 1 allow you to monitor what the power supply is reading from the input connector.

Under some conditions, it is desirable to ignore potentially damaging conditions. For this purpose the power supply provides a battle override function in the system status register. If bit 7 in the status register is set, then any non-recoverable events that would normally shut down the supply will not do so.

Event messages are still sent, but the power supply will continue to operate until the conditions cease to exist or it fails.

In order to enable battle override mode, the command message must include the exact same data byte three times in a row within the message where normally only a single byte would be needed.

| Bit | Name        | Condition                                                                                                             | Default           |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------|-------------------|

| 7   | ВО          | Battle override; see description                                                                                      | 0                 |

| 6   | FAIL        | If set to 1 by System Manager, a fault condition will clear this bit.                                                 | 0                 |

| 5   | OT Warning  | If set to 1 by System Manager,<br>an OT fault will clear this bit.                                                    | 0                 |

| 4   | SW Priority | Software Priority  1 = STATUS REGISTER overrides hardware inputs for INHIBIT* and ENABLE*  0 = Hardware is in control | 0                 |

| 3   | *SW lnh     | Software Inhibit  0 = Inhibit active (same as hardware input state)                                                   | 0                 |

| 2   | *SW En      | Software Enable  0 = Enable active (same as hardware input state)                                                     | 0                 |

| 1   | *HW lnh     | Status of ENABLE* pin (read only)                                                                                     | From<br>backplane |

| 0   | *HW En      | Status of INHIBIT* pin (read only)                                                                                    | From<br>backplane |

| IPMB<br>Byte<br>Number | Hex<br>Byte | Clock Pulses<br>Generated By | Data Pulses<br>Generated By | Comment                                                                                                                       |

|------------------------|-------------|------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 1                      | 40h         | Requestor                    | Requestor                   | Address byte of power supply with hardware address 0x20 and LSB read/write low.                                               |

| 2                      | 55h         | Requestor                    | Requestor                   | Command byte. Request 1                                                                                                       |

| 3                      | 80h         | Requestor                    | Requestor                   | Only set BO.                                                                                                                  |

| 4                      | 2Bh         | Requestor                    | Requestor                   | Zero checksum generated from IPMB bytes 2 – 3 and Stop Bit.                                                                   |

| 5                      | 40h         | Requestor                    | Requestor                   | Address byte of power supply with hardware address 0x20 and LSB read/write low.                                               |

| 6                      | 55h         | Requestor                    | Requestor                   | Command byte. Consecutive request 2                                                                                           |

| 7                      | 80h         | Requestor                    | Requestor                   | Only set BO. Byte identical to IPMB byte 3.                                                                                   |

| 8                      | 2Bh         | Requestor                    | Requestor                   | Zero checksum generated from IPMB Bytes 6 – 7 and Stop Bit.                                                                   |

| 9                      | 40h         | Requestor                    | Requestor                   | Address byte of power supply with hardware address 0x20 and LSB read/write low.                                               |

| 10                     | 55h         | Requestor                    | Requestor                   | Command byte. Consecutive request 3                                                                                           |

| 11                     | 29h         | Requestor                    | Requestor                   | Only set BO. Byte identical to IPMB byte 3.                                                                                   |

| 12                     | 2Bh         | Requestor                    | Requestor                   | Zero checksum generated from IPMB bytes 10 – 11. Battle override enabled after byte 12 is processed by the power supply IPMC. |

| 13                     | 40h         | Requestor                    | Requestor                   | Address byte of power supply with hardware address 0x20 and LSB read/write high.                                              |

| 14                     | 55h         | Requestor                    | Requestor                   | Command byte.                                                                                                                 |

| 15                     | ABh         | Requestor                    | Requestor                   | Zero checksum generated from IPMB byte 14 and Stop Bit.                                                                       |

| 16                     | 41h         | Requestor                    | Requestor                   | Address byte of power supply with hardware address 0x20 and LSB read/write high.                                              |

| 17                     | 55h         | Requestor                    | Requestor                   | Echo Command byte.                                                                                                            |

| 18                     | 82h         | Requestor                    | Power Supply                | Status register byte showing power supply is in battle override, enabled and not inhibited.                                   |

| 19                     | 29h         | Requestor                    | Requestor                   | Zero checksum generated from IPMB bytes 17 – 18 and Stop Bit.                                                                 |

**Table 7** — PC communication example for battle override

# **IPMI** Interface

The data interface is compliant with the requirements of VITA 46.11, VITA 62 -2016 and the IPMI v2.0 specifications. This section shows product specific information such as a sensor list and their coefficients.

#### **Data Format**

Four constants are used to calculate a real world value from the single byte variable returned in the response. The four constants are used in the equation Interpreting Received Values

$$y = (Mx + (B \bullet 10^{KI})) \bullet 10^{K2}$$

Where:

**y** the converted reading

**x** the raw sensor reading

**M** the signed integer multiplier

**B** the signed additive offset

**K1** signed exponent for constant B (sets decimal point for B)

**K2** signed result exponent (sets decimal point for y)

#### **Sensors and Constants**

The list of sensors and coefficients can also be retrieved by the chassis manager by querying the "Sensor Data Record" (See VITA 46.11).

| Sensor<br>Number | Hex | Sensor Name                 | Type<br>Code | Description              | SI<br>Units | M  | В  | K1 | К2 |

|------------------|-----|-----------------------------|--------------|--------------------------|-------------|----|----|----|----|

| 2                | 02h | FRU Health                  | F2h          | 04h - Predictive Failure | Discrete    |    |    |    |    |

| 3                | 03h | FRU Voltage                 | 02h          | 05h - Limit Exceeded     | Discrete    |    |    |    |    |

| 4                | 04h | FRU Temperature             | F3h          | 6Fh - Sensor Specific    | Discrete    |    |    |    |    |

| 7                | 07h | Input Voltage               | 02h          |                          | V           | 20 | 90 | 1  | -2 |

| 8                | 08h | VS1, +12V Voltage           | 02h          |                          | V           | 20 | 90 | 2  | -3 |

| 11               | 0Bh | AUX, +3.3VAUX Voltage       | 02h          |                          | V           | 10 | 20 | 2  | -3 |

| 14               | 0Eh | Input Current               | 03h          |                          | А           | 40 | 0  | 0  | -2 |

| 15               | 0Fh | iS1, +12V Current           | 03h          |                          | А           | 32 | 0  | 0  | -2 |