# **Thermal Models of Vicor Power Components**

Kim Mosley

This paper describes the circuit models that have been created for Vicor products to allow engineers to estimate the maximum internal temperature of the power component when operating under known electrical conditions in a defined thermal environment.

### **Thermal circuit models**

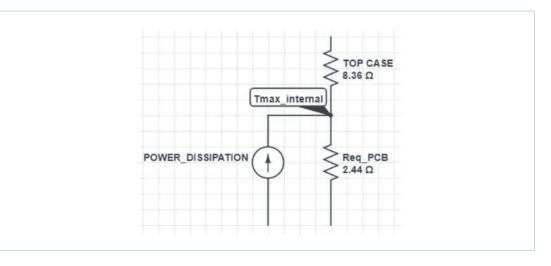

Thermal circuit models are analogous to electrical circuits and contain resistors, current sources and voltage sources. Electrical resistors are replaced in this analogous circuit model with thermal resistances in units of degrees Celsius per watt (°C/W). A current source is utilized as analogous to a heat source in units of watt (W). The voltage source is utilized as an analogous temperature source in this circuit model with units of degrees Celsius (°C).

The underlying calculations are the same as those used in the Vicor suite of <u>online tools</u>. The thermal data is also the same, but the online tools provide more extensive temperature-dependent electrical performance modeling.

### **Maximum internal temperature**

There is a single node in these circuit models that represents the maximum internal temperature of the product. This maximum internal temperature node is a virtual representation of the maximum internal temperature within the device during any and all electrical and thermal conditions – as such, it may change location as electrical and thermal operating conditions change. The maximum internal temperature derived from these circuit models should be less than the maximum temperature in the operating temperature range for the Vicor power component under consideration.

Vicor products contain an array of internal components including control ICs, switching FETs, resistors, capacitors and more. Although these components may have different maximum operating and/or maximum survival temperatures as rated by the manufacturer, they all reside on the same printed circuit board (PCB) inside the device.

The laminate used in the PCB has a maximum operating temperature (MOT) as determined by the manufacturer of the laminate and this is the primary determination of the maximum value in the range shown as product internal temperature on the data sheet. Exceeding the MOT temperature in the laminate does not cause immediate destruction of the material. Rather, the MOT is typically a mathematical evaluation of the temperature at which the laminate material will lose a certain percentage of its physical and/or electrical properties after thousands of hours of exposure.

It is this MOT that is the primary determination of the maximum value in the product internal temperature range on the data sheet. Product compliance ratings are based on internal temperature of the product being within this operating range. While product can be operated up to the maximum of this internal temperature range, it is always better to operate any electronic product at as low a temperature as possible. The power FETs utilized inside the product will typically have a lower drain-to-source resistance with lower temperature. Electrical resistance of copper also decreases with reduced temperature – copper resistance at 100°C is about 30% higher than the resistance at 25°C. The result of this is that product will typically have a greater efficiency at a lower operating temperature. Reliability and operating life also improve with lower operating temperature, as it is a generally accepted rule-of-thumb that a 10°C decrease in electronics operating temperature doubles reliability and operating life.

### **Creation of circuit models**

To create these circuit models, finite element software is utilized to perform a detailed thermal simulation of the power component under a variety of thermal and electrical operating conditions. The simulation contains details of the complex copper and laminate geometry of the PCB as well as details of the geometry and material for FETs, cores and other components inside the device.

The overall dissipation is broken down to the power dissipation of all the major internal components in the power component. Multiple thermal simulations are run and the temperature rise of all components internal to the product is determined at these varied conditions. The circuit model and resultant resistance values are then determined so the circuit model can estimate the maximum internal operating temperature of the device under this variety of thermal and electrical operating conditions. These circuit models are shown on the data sheet along with the thermal resistance values derived.

Testing of the product is performed to validate the temperature results obtained from the finite element simulation.

### **Circuit model – ChiPs**

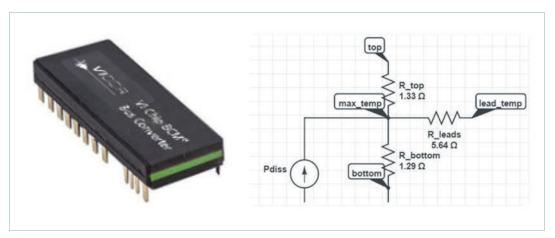

For the through-hole style of ChiP<sup>™</sup>, Figure 1 shows a picture of the package, along with a representative circuit model. Note the maximum internal temperature in the device is represented by a single temperature node.

ChiP and circuit model for 6123 BCM K 1/8

### **Circuit model - VIAs**

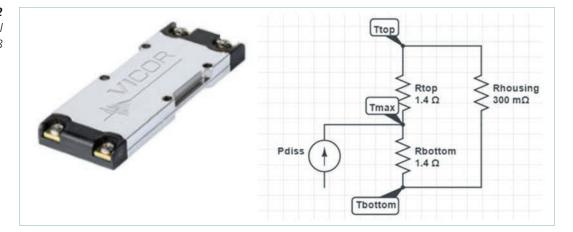

VIA<sup>TM</sup> packaging technology circuit models are similar in that they contain a single node to represent the maximum internal temperature of the component. The resistance network from this node to external boundaries is slightly different. Figure 2 below shows a picture of a VIA and a typical circuit model.

**Figure 2** VIA package and circuit model for VIA BCM<sup>®</sup> K1/8

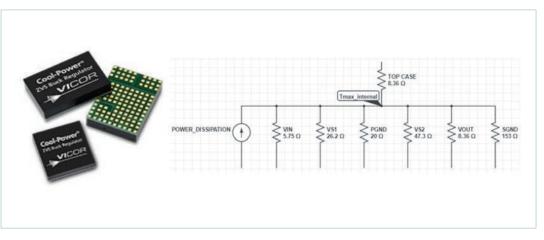

## Circuit model – Cool-Power® ZVS Switching Regulators

Vicor supplies a diversity of switching regulators in a SiP-style package. A picture of some of these along with a representative circuit model is shown in Figure 3 below.

Figure 3

Cool-Power regulators and representative circuit model

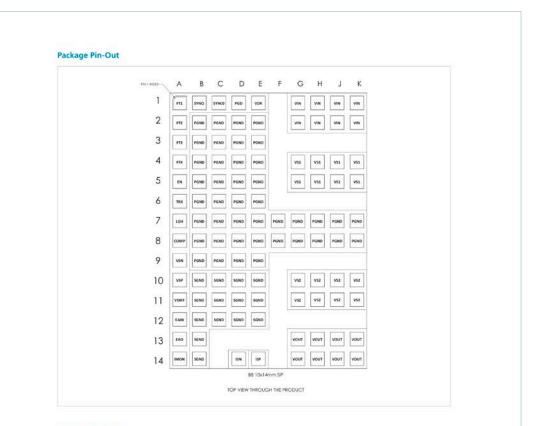

The resistance values shown below the " $T_{MAX\_INTERNAL}$ " node in the circuit model represent connections to the PCB as identified in the data sheet. For the same circuit model shown in Figure 3 above, Figure 4 below shows how these connections are arranged on the body of the SiP.

#### Large Pin Blocks

| Pin Block Name | Group of pins                                                                                                    |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------|--|--|

| VIN            | G1-2, H1-2, J1-2, K1-2                                                                                           |  |  |

| VS1            | G4-5, H4-5, H4-5, K4-5<br>82-9, C2-9, D2-9, E2-9, F7-8, G7-8, H7-8, J7-8, K7-8<br>G10-11, H10-11, J10-11, K10-11 |  |  |

| PGND           |                                                                                                                  |  |  |

| V52            |                                                                                                                  |  |  |

| VOUT           | G13-14, H13-14, J13-14, K13-14                                                                                   |  |  |

| SGND           | B10-14, C10-12, D10-12, E10-12                                                                                   |  |  |

*Figure 4 SiP connections to PCB*  The resistance connections to the PCB are shown separately to distinguish the relative impact each connection has on cooling the SiP. For the example shown in Figure 3, it can be seen by their lower thermal resistance values that the  $V_{\rm IN}$  and  $V_{\rm OUT}$  connections represent the primary conduction paths for cooling the SiP – the designer may want to dedicate additional copper in their PCB to improve thermal conduction to these connections. For the case where only a single PCB temperature can be identified, the circuit model would simplify to that shown in Figure 5 below.

### Figure 5

Simplified circuit model for SiP shown in Figure 4

The resistance values utilized in the circuit models are also contained in the data sheets. For example, the 6123 BCM<sup>®</sup> K 1/8 thermal resistance values from the component's data sheet are shown in Figure 6.

### Figure 6

6123 BCM K 1/8 thermal resistance values

|                                |                       | Thermal                                                                                             |     |      |     |      |

|--------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Operating temperature          | TINTERNAL             | BCM400P500T1K8A30 (T-Grade)                                                                         | -40 |      | 125 | °C   |

|                                |                       | BCM400P500M1K8A30 (M-Grade)                                                                         | -55 |      | 125 | °C   |

| Thermal resistance top side    | <b><b><b></b></b></b> | Estimated thermal resistance to<br>maximum temperature internal<br>component from isothermal top    |     | 1.33 |     | °C/W |

| Thermal resistance leads       | <b><i><b></b></i></b> | Estimated thermal resistance to<br>maximum temperature internal<br>component from isothermal leads  |     | 5.64 |     | °C/W |

| Thermal resistance bottom side |                       | Estimated thermal resistance to<br>maximum temperature internal<br>component from isothermal bottom |     | 1.29 |     | °C/W |

# Use of circuit models

For more information about the use of these circuit models, see Vicor's white paper titled "Use of circuit models in Thermal Calculations."

Contact Us: http://www.vicorpower.com/contact-us

### Vicor Corporation 25 Frontage Road Andover, MA, USA 01810 Tel: 800-735-6200

Tel: 800-735-6200 Fax: 978-475-6715 www.vicorpower.com

### email

Customer Service: <u>custserv@vicorpower.com</u> Technical Support: <u>apps@vicorpower.com</u>

©2018 Vicor Corporation. All rights reserved. The Vicor name is a registered trademark of Vicor Corporation. All other trademarks, product names, logos and brands are property of their respective owners.