电流倍增器:为 AI 处理器及其他严苛应用供电的明智之选

AI 处理器需要解决低电压、高电流的严苛挑战,这将会导致电源系统设计产生瓶颈。了解 Vicor 的电流倍增技术如何改变这一现状

构建高性能 PDN,为电源系统工程师提出了一系列相互关联的重要挑战。Vicor 的创新架构将开启尚未开发的超级计算性能的大门,满足当今最常见的应用需求。

作者:Doug Ping,Vicor 高级首席应用工程师

不断增加的计算工作复杂性和负载多样性需要巨大的处理能力。无论是用于云计算数据中心还是本地应用,新一代处理器都能提高吞吐量、降低时延。然而处理器的发展需要供电的发展。因此,电源往往限制了获得最高处理器性能的能力。

近期疫情使网上购物、流媒体和居家办公激增,超大型服务及零售供应商扩大了其产能。但为了更全面地了解数据中心的增长,应该将其置于其它几个推动因素的背景下。过去 10 年出现的主要技术发展推动趋势包括物联网 (IoT)、人工智能 (AI)、边缘机器学习 (Ml),以及运营技术 (OT) 工作量的指数增长等。工业 4.0 等工业运营性能改善举措导致 OT 部署大幅度增加。这些因素需要更高的计算功能,但它们也导致了更多样化、更高要求的工作负载。

对数据中心提供灵活、可扩展的计算基础架构的需求日益增多,这些基础架构能够支持高动态工作负载,从而可提供云计算服务或本地服务。最近趋势要求的一些计算任务的性质包括低时延、峰值神经网络算法和搜索加速。如现场可编程门阵列 (FPGA)、图形处理单元 (GPU) 和神经处理单元 (NPU) 等,曾经很少在数据中心使用的、高度优化的专业处理器件,现已变得非常普遍。此外,集群 AI 神经网络推断引擎等新一代专用集成电路 (ASIC) 也需要完成高性能计算任务。

处理器技术的进步帮助高性能计算推动了任务吞吐量的发展,从而可提供灵活性以适应更多的工作负载多样性。然而,技术的增益通常取决于同步发展的系统的其它方面。

在半导体行业,变化是不可避免的。一种更小的全新硅芯片工艺节点投入生产,下一次迭代也就不远了。更小几何尺寸允许在给定空间中构造更多单独的半导体门。虽然 65nm 和 55nm 工艺节点仍然和往常一样,主要用于许多集成电路 (IC),但 ASIC、FPGA、GPU 和 NPU 等高性能计算器件一般基于 12nm 以下的工艺节点,因此 7nm 和 5nm 工艺节点越来越受欢迎。客户已经在排队购买使用 3nm 工艺节点的先进高性能处理器。

通过缩小单个门的尺寸来增加其密度,凸显了管理新处理器热特征的限制。降低栅极工作电压时,一个被称为电压缩放的过程有助于减少每个晶体管的散热,但整个封装的热管理仍然至关重要。

高性能处理器一般会在其最大时钟速率下运行,直到热限制需要将其限制回来为止。电压缩放显示,最复杂的 5nm 工艺节点器件的核心电压降至 0.75V ,预计 0.65V 工艺节点的核心电压将进一步降至 0.23V。让供电挑战更加严峻的是,许多器件需要多个不同电压并精心排序,以避免永久性损坏。

前沿 GPU 通常有几千亿颗晶体管,因此电流需求已变得很大,达到了数百安培。对于集群 AI 处理器而言,1000A 的需求并不罕见。目前的趋势是处理器的功耗每两年翻一番(图 1)。

向这种高功耗器件供电的另一个方面是:其工作负载可在一微秒内发生变化,这可能会在整个供电网络 (PDN) 中产生巨大的瞬态。

图 1:在大型计算系统中,供电和电源效率已成为最受关注的问题。随着处理复杂 AI 功能的 ASIC 和 GPU 的出现,整个行业的处理器功耗已大幅提升。随着 AI 性能用于大规模学习及推断应用部署,机架功耗也随之增加。在大多数情况下,由于新 CPU 需要消耗的电流越来越多,供电现已成了计算性能的限制因素。供电不仅涉及配电,而且还涉及效率、规模、成本和散热性能。

我们强调过,半导体工艺技术的进步,为 PDN 带来了几个具有挑战性的条件。但并不是所有这些都是技术性的。例如,这些前沿处理器件的物理尺寸将占用相当大比例的可用电路板空间。复杂的是,电路板空间通常受限于行业标准外形。

随着电路板尺寸的限制的加剧,高性能计算器件的本质要求支持各种 IC,例如靠近处理器布置的存储器和光信号收发器等。此外,由于流耗的剧增以及核心电压的降低,这种方法也适用于负载点 (PoL) 电源稳压器。大电流 PCB 布线电路的影响会产生 I2R 损耗,清晰可辨的压降完全能对处理器性能产生影响,甚至更糟糕的是:会带来不稳定的行为。此外,PoL 稳压器也需要高功率效率,才能进一步防止热管理并发症(图 2)。

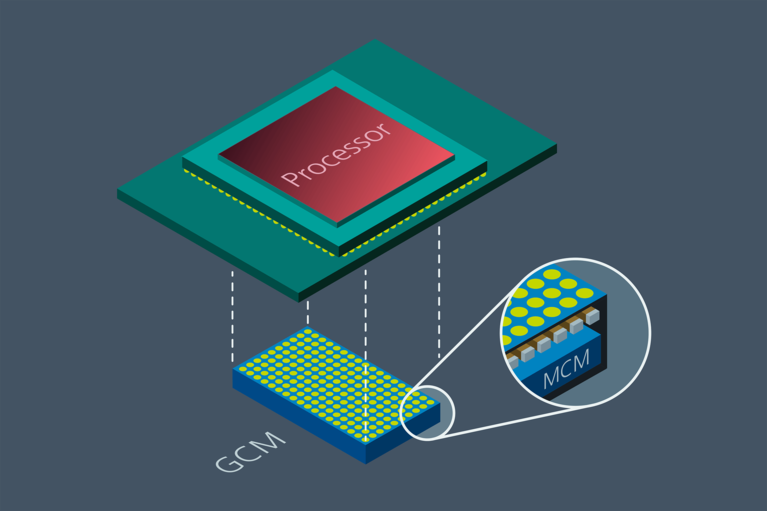

图 2:VPD 进一步消除了配电损耗和 VR PCB 电路板面积的消耗。VPD 与 Vicor LPD 解决方案设计类似,在电流倍增器或 GCM 模块中增加了对旁路电容的集成。

电路板空间有限加上将稳压器靠近处理器安装的需求,带来了架构网络 PDN 的全新创新方法。

随着处理器技术的不断发展,架构高效 PDN 将为电源系统工程师带来三项相互关联的重要挑战。

领先的高性能处理器可消耗数百安培的电流。为处理器提供足够的电源容量不仅涉及布置负载点转换器的位置的物理约束,而且还涉及将电源从边缘连接器导入转换器的 PCB 布线的复杂抉择。由极为动态的工作负载引起的高电压瞬态,可能会干扰其它系统组件。

影响电源效率的因素有两个:I2R 损耗和转换效率。PCB路径对低压信号和数字逻辑走线连接是理想选择,,但对于大电流而言,无论多短,它们可能都代表显著的电阻损耗。这些 I2R 损耗会降低提供给处理器的电压,并引起局部发热。处理器卡上有数百个其它组件,所以电源走线的大小是有限制的,因此尽量靠近处理器布置转换器是唯一可行的替代方案。

转换器的功效是其设计的一个属性。开发高效 PoL 转换器是一项专业技能,涉及一种迭代方法,以了解从无源器件到半导体每个组件)的损耗。我们之前已经强调过,损耗表现为需要消散的热量。PoL 转换器模块设计人员运用他们的设计专业技术和专业知识优化模块的内部设计,以实现等温封装。

面对 PDN 的挑战,一些电源架构师可能会选择为处理器创建一个分立式 PoL 转换器,以便精心定制 PDN。然而,尽管这可能是一种可行的解决方案,但它实际上增加了复杂性。分立式设计会增加物料清单 (BOM),带来采购更多组件的需求以及相关物流成本和供应链成本。此外,这种方法还需要更多的工程设计工作,增加无法收回的支出 (NRE),并延长开发和测试时间。相反,模块化方法经过精心设计,可优化高性能处理器的电源。散热良好的集成型电源模块可显著简化电源设计,从而可减少 BOM,增加修改的灵活性,并可促进开发。电源模块紧凑、功率密集并可轻松缩放。

为了应对当前常见的 PDN 挑战,Vicor 提供了两种符合今天最常见情况的方案。

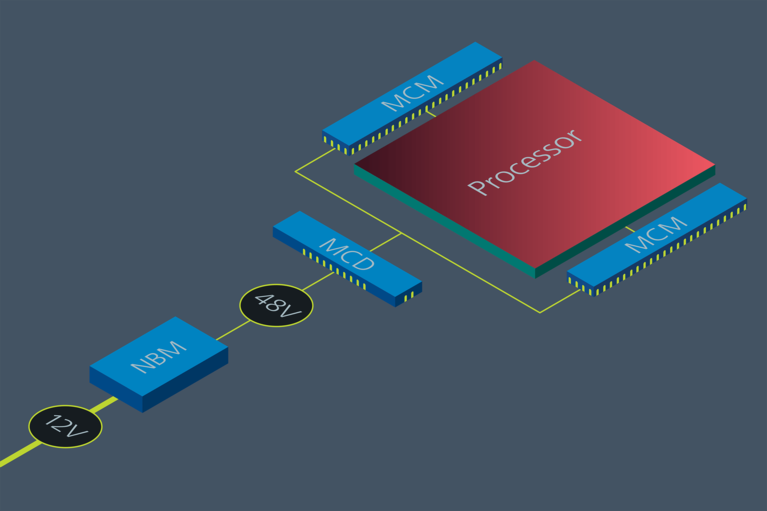

将 12V 系统连接至 48V 系统。对于需要更高效率以及更多电源的原有系统,Vicor 提供了一种使用双向 NBM™ 非隔离母线转换器的简单选项。NBM 可在 48V 与 12V 之间实现高效转换,因此既可将原有电路板整合在 48V 基础架构中,也可将最新 GPU 整合在原有 12V 机架中(图 3)。

图 3:将 12V 系统连接至 48V 系统。对于需要更高效率以及更多电源的原有系统,Vicor 提供了一种使用双向 NBM™ 非隔离母线转换器的简单选项。NBM 可在 48V 与 12V 之间实现高效转换,因此既可将原有电路板整合在 48V 基础架构中,也可将最新 GPU 整合在原有 12V 中。

48V 至负载点。Vicor 合封电源 (PoP) 解决方案可将主板电阻降低至 1/50,将处理电源引脚减少至1/ 10。利用分比式电源架构 (FPA™),Vicor 可通过两种专利解决方案,即横向供电 (LPD) 和垂直供电 (VPD),最大限度减少“最后一英寸”电阻。这两种解决方案可帮助处理器实现以前无法实现的性能,为当前呈指数级增长的 HPC 处理需求提供支持。

对数据中心、边缘计算以及物联网的需求并没有减弱。大数据需要的处理速度是前所未有的。当前的最高处理速度在 9 个月后将变得太慢,供电将再次成为焦点。寻找提高吞吐量并缩短时延的新方法是一项长期挑战。确定一个高度灵活的可扩展解决方案,是完成这道难题的最后一步。这将最大限度减少重新设计的次数,并简化未来的修改。模块化方法适应了当前及未来高性能计算的所有方面。

本文最初由 Power Semiconductors 发表。

Doug Ping 在电源行业拥有超过 26 年的丰富设计及应用工作经验,在 Vicor 已工作 21 年。自 2007 年以来,他一直专注于数据中心和自动驾驶汽车应用的电源解决方案。

作者:Doug Ping,Vicor 高级首席应用工程师