ジョー・アギュラー /プリンシパルエンジニア・シニアマネージャー

本稿では、高性能のPCBレイアウトの基本についてJoe Aguilar が解説します。放熱設計のアプローチや、電力供給ネットワーク(PDN)の概要、大電流を低インピーダンスで配線するための戦略、効果的なデカップリング容量を決めるときに検討すべき重要なポイントを解説します。

HPC(ハイ・パフォーマンスコンピューティング)のための電源設計:

極めて重要なPCB設計

電源システムを設計する場合は、通常、電力源から負荷に電力を供給するために必要な、コンバータやディスクリート部品や、それらの付属部品に重点を置きます。プリント回路基板(PCB)は従来、部品を実装して配線する板であり、PCB内の各所に生じる小さな電力損失やインピーダンスは、一般的に、フィードバック回路や制御回路で補正します。しかし近年は、人工知能(AI)やスーパーコンピュータ用のプロセッサのような電力密度が高い負荷は、非常に精密で高速な動作をするため、PCBを含めたすべてのコンポーネントの性能を最大限に発揮させる必要があります。

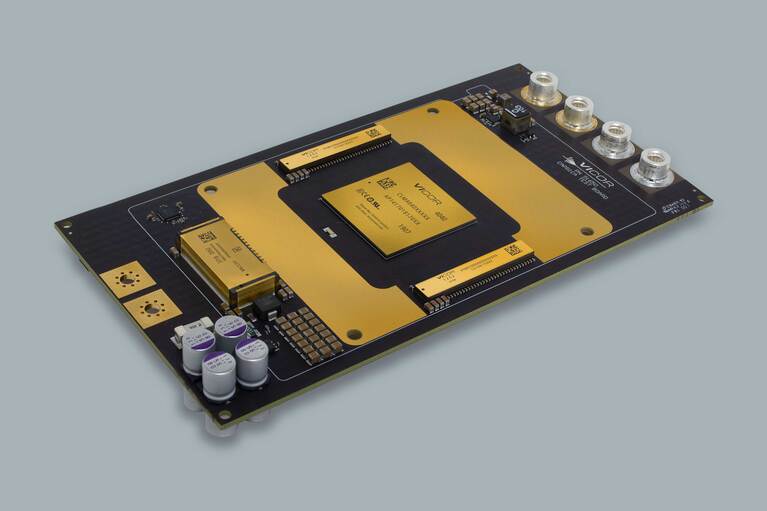

電圧レギュレーションの精度が高く、かつ過渡応答のスルーレートが極めて高い電源システムでは、システム内の非常に小さいインピーダンス(電圧降下や電力損失の要因)が重大な悪影響を引き起こします。したがって、高性能な電源システムを実現するためには、PCBレイアウトが極めて重要です。本稿では、高性能のPCBレイアウトについて、基本原則を簡単に説明します。その中には、放熱の設計、電力供給ネットワーク(PCB)の概要、大電流を低インピーダンスで配線する方法、デカップリングコンデンサを配置するときに検討すべき重要事項が含まれます。図1は、本稿で紹介する試験とデモ用にVicorが設計したPCBです。

図1: Vicorのテストボード。PRM™ レギュレータと2つのVTM™ カレントマルチプライヤを高密度PCBに実装しており、HPC用プロセッサをシミュレートする負荷モジュールに給電します。作動時は、VTMと負荷モジュールの上に冷却プレートまたはヒートシンクを、PRMには別のヒートシンクを取り付けます。

放熱設計

電源システムの設計における放熱設計の目的は、ジャンクションから発生する熱を周囲の空気へ効率よく稼働させることです。ある程度の熱は自然に移動しますが、通常はヒートシンクや冷却ファンを取り付ける必要があります。電力密度の高いシステムで、PCB自体を熱伝導体として最大限に利用するためには、設計の初期段階で、PCBに注目して熱の伝導を詳しく分析する必要があります。

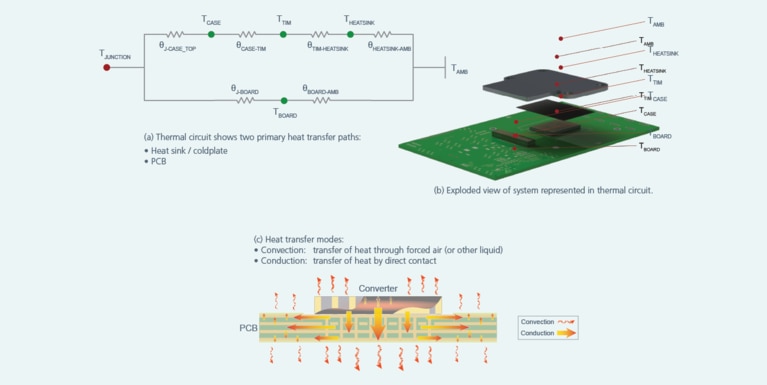

図2: 発熱する部品を高密度に実装するシステムの放熱設計において、発熱部品からPCBまでとPCB自体の熱伝導は重要であり、最も効果的な放熱方法を見極めるためには等価回路モデルを用います (a) (b)。熱の伝導と対流の両方を最適に組み合わせるのが、優れた放熱設計です (c)。

電源システムにおける主な発熱源は、コンバータなど能動部品の内部のジャンクションです。熱モデルでは、等価回路の端に配置したノードで表現されています (図2(a) 参照)。内部のジャンクションから発生する熱は、電源システムの外の空気に達するまでの間に、部品や材料を通過しますが、こちらの部品や材料は熱の流れを妨げる抵抗として働きます。放熱の等価回路は、コンバータ内部のジャンクションから発生する熱が伝わる経路のうち、もっとも分かりやすいものを示しています。それは、熱がコンバータのケースを通り、熱伝導材料 (TIM) を通って最終的にヒートシンクから周辺空気へ放熱される経路です。もう一つ、あまり目立たないPCBの中を通る放熱経路が、並列に示してあります。この2つめの放熱経路は、見落としやすいのですが、電力密度の高い電源システムでは極めて重要です。

配線やランドの熱抵抗値はそれぞれ異なるため、熱モデルはかなり複雑になります。ただし熱モデルが複雑であっても、ジャンクションから伝わる熱は、主に熱抵抗の最も低い経路を通して放熱します。放熱設計ではこの点に注意して、該当する経路の銅の量を増やして熱伝導性能を最大限に良くします。つまり、放熱性能を上げるための、最低限必要となる表面層の銅プレーンの拡大と、サーマルビアの配置を行います。サーマルビアには、積み上げのタイプや埋め込みタイプなど、様々な種類があり、目的に合わせて選びます。VIPPOも従来のスルーホールビアも、放熱設計に用いることで、放熱の性能を向上することができます。

電力供給ネットワーク (PDN) の概要

HPC(ハイ・パフォーマンスコンピューティング)用の電源システムでは、電力供給ネットワーク(PDN)のインピーダンス、特にPCB内のインピーダンスは極めて重要です。システムの動作周波数が非常に高いからです。一般的なHPC用の電源システムでは、PDNは、電圧レギュレータの出力と電圧検知ポイントとの間にある、いくつかの要素で構成されます。電圧検知ポイントは、CPU内のダイ上か内部のBGA接続部にあります。PDNを構成するディスクリート部品としては、バイパスコンデンサ、デカップリングコンデンサと、関連するビア、BGA接続部があります。高性能スーパーコンピュータのプロセッサによって生じる高周波の負荷変動は、非常に速いため、制御ループによってPDNの影響を補償することは困難です。そのため、システムの設計においてPDNは重要です。

図3: 電源(レギュレータ)とCPU(負荷)の間のPDNはディスクリートの部品で構成されます。電源の性能は、これらのディスクリート部品のインピーダンスの影響を受けます。特に高周波で負荷変動が大きいときは、その影響は深刻です。

大電流の配線: PDNのインピーダンスを低減

PCBの積層構成とレイアウトを前もって定義することは極めて重要です。全体のレイヤー数、電源とグランド専用のレイヤー数、銅箔の厚さなどです。次に、連続するグランドプレーンに沿って配線する信号線のレイヤーを決めます。そして、インピーダンス制御が必要な配線や、寄生容量の上限がある配線、その他にも特に注意すべき配線があれば、これらを配線するレイヤーをすべて決めます。この手順を正しく行うことは、1000アンペア以上の大電流に対するプロセッサ向けのPCBを設計する上で欠かせません。

設計を改善するために使うシミュレーションを簡単に使うテクニックにより、PCB設計の初期段階のスピードアップが可能です。銅プレーンの面積抵抗率を見積もるには、スクエアメソッドという簡単で効果的な方法があります。スクエアメソッドを使うと、隣接する電源プレーンやリターンプレーンのインダクタンスの概算もできます。

図4: 電源プレーンの抵抗とインダクタンスを見積もるスクエアメソッド

ビアは薄い銅板を管状に巻いたものと考えることができるので、ビアの抵抗値とインダクタンス値は、幾何学的に、簡単な計算で求めることができます。ビアの抵抗値 (R) は、銅メッキの抵抗率 (r) にビアの長さ (L) を掛けて、銅メッキの断面積 (A) で割ることで得られます。

図5: ビアの抵抗値は、簡単な幾何学的な計算で概算することができます。

寄生容量も、PCBに大きなインピーダンスが現れる原因になるため、シミュレーションで考慮する必要があります。抵抗やインダクタンスの場合と同様に、PCB内の寄生容量は、基本的な物理特性から概算します。一般的に、平行に配置した導体プレーン間の寄生容量は、表面積に比例し、誘電体の厚さに反比例します。

デカップリングコンデンサ

高電力密度の電源システムの、高周波のスイッチングノイズに対するフィルターでは、デカップリングコンデンサを慎重に選ぶ必要があります。このタイプのアプリケーションでは、ESRが極めて低く、自己共振周波数がある程度高いコンデンサが必要です。もしこの条件から外れると、ESLに起因してインピーダンスが誘導性になり、コンデンサが高周波ノイズのフィルターとして機能しなくなります。コンデンサの容量値はあまり重要ではありません。

図7: 高周波スイッチングのノイズに対応する、低インピーダンスのフィルターを実現するためには、コンデンサの選択とビアの配置が極めて重要です。

最初の課題は低 ESR かつ 低 ESL の実現です。それには小型で低インダクタンスの長編電極のコンデンサを使い、プラスとマイナスの端子を近づけて配置して、自己共振周波数が高くなるようにします。ループのインダクタンスを最小限に抑えるために、部品とビアの両方を慎重に配置することが重要です。

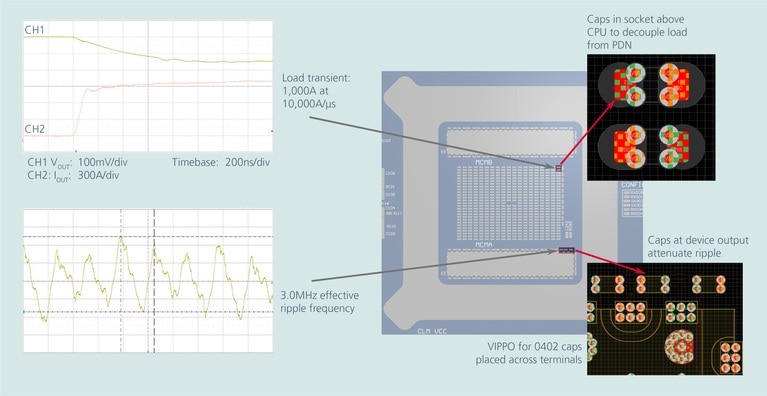

例えば、1000Aの負荷変動が10,000A/µs の電流変化速度で発生する場合、これに対応するシステムでは、電源モジュールの近くに配置した 0402 サイズのデカップリングコンデンサで電源のリップルを減衰させ、ソケット内の別のコンデンサによりPDNと負荷をデカップリングしています。

図8: 適切なコンデンサを選び適切な場所に配置して、性能が出るようにビアを使うことで、10,000A/µs 、1000Aの負荷変動に対応します。

今日の高性能プロセッサでは、電源電流は増え続けており、電圧の要求精度はますます高くなるため、HPCやAIのためのPDNの設計には高度な技術が求められます。したがって、冷却構造とPDNの設計における最新のモデリング・概算の技術と、高性能部品の選択と配置の基準が必要になります。

Vicor のオンデマンド・ウェビナー 最適なPCBレイアウトと放熱設計技術 もあわせてご参照ください。

ジョセフ・アギュラーは、VIcorのDC-DC製品アプリケーションのシニアマネージャーです。パワーエレクトロニクス業界でアプリケーションエンジニアとして防衛、産業、通信、照明、コンピューティングなどの幅広い分野で15年以上の経験を積んできました。近年は主にHPCの製品開発とリファレンス設計に注力しています。アギュラーは、マサチューセッツ州スプリングフィールドのウェスタンニューイングランド大学を卒業し、BSEE(電気工学学士)を取得しています。

ジョー・アギュラー/ プリンシパルエンジニア・シニアマネージャー